MVME1X2P4 boards use SDRAM (Synchronous DRAM) in place of DRAM. The MVME162P4’s 16/32MB shared SDRAM is configurable to emulate either of the following memory models:

The two memory controllers modeled in the Petra ASIC duplicate the functionality of the “parity memory controller” found in MC2 ASICs as well as that of the “single-bit error correcting/double-bit error detecting”memory controller found in MCECC ASICs. Board firmware will initialize the memory controller as appropriate.

If the Petra ASIC is supporting MVME1X2P4 functionality, firmware will enable the parity (MC2) memory controller model. If the Petra ASIC is supporting MVME1X2P2 functionality, firmware will enable either the parity or the MCECC memory controller model, depending on the board configuration. Board configuration is a function of switch settings and resistor population options.

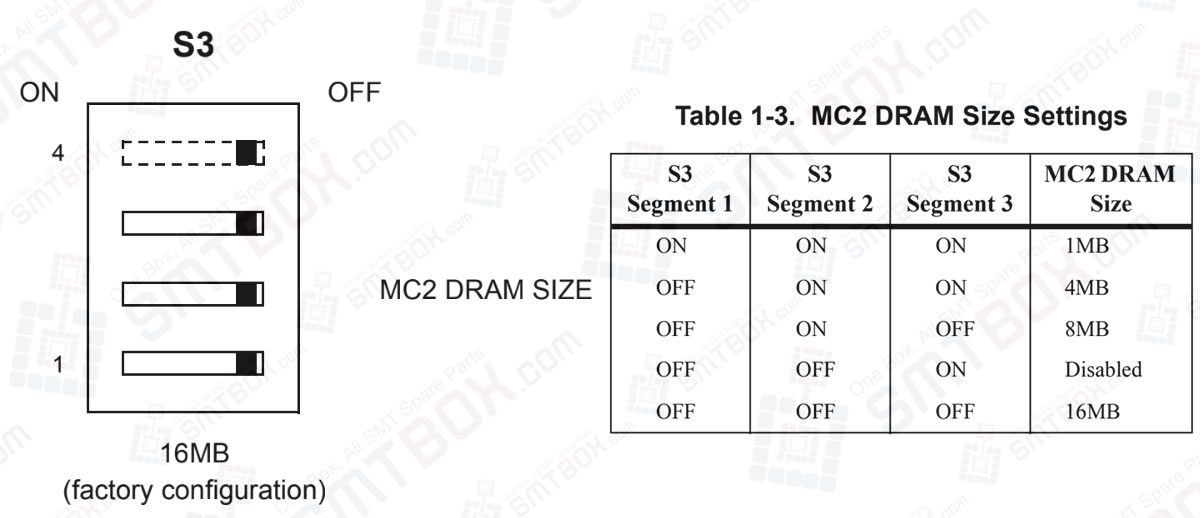

S3 comes into play in the MC2 memory controller model. S3 is a four segment slide switch whose lower three segments establish the size of the parity DRAM (segment 4 is not used.) Refer to the illustration and table below for specifics.

Notes As shown in the preceding table, the Petra/MC2 interface supports parity DRAM emulations up to 16MB. For sizes beyond 16MB, it is necesary to use the MCECC memory model.

For access to the MCECC registers, you must first disable the MC2 interface by setting S3 to 001 (Off/Off/On). Further details on selecting the MCECC emulation can be found under MCECC DRAM Size (S6).

If you modify the switch settings, you will need to execute env;d

Note: Model Number: MVME162P-344SE, Characteristics: 32MHz 68040, 16MB SDRAM, 2 SIO, 4 DMA IP, SCSI/Ethernet is used on Universal UIC HSP4797L Hitachi Sanyo TCM-X100